The PCI bus standard was originally introduced by Intel in 1992. It is a 32-bit parallel bus with a maximum transmission speed of 133 MB/s.

Before the introduction of PCI, computer devices were typically connected using the ISA (Industry Standard Architecture) bus. However, the ISA bus's slow transmission speed limited computer system performance and scalability. Therefore, the introduction of the PCI bus is considered a major milestone in the development of computer technology.

With the continuous advancement of computer technology, PCI bus standards have been continuously upgraded. In 1993, PCI 2.0 was introduced, adding a 66 MHz transmission speed, bringing the maximum transmission speed to 266 MB/s. In 1995, PCI 2.1 was introduced, adding support for power management and hot-swap functionality. In 1998, PCI 2.2 was introduced, adding support for 64-bit data transmission.

The PCI bus standard has been continuously upgraded, becoming one of the most commonly used bus standards in computer systems. However, as the performance and scalability requirements of computer systems continue to increase, the PCI bus standard is no longer able to meet the needs of modern computer systems. Therefore, the PCI Express (PCIe) bus standard has gradually replaced the PCI bus standard and become one of the most commonly used bus standards in modern computer systems.

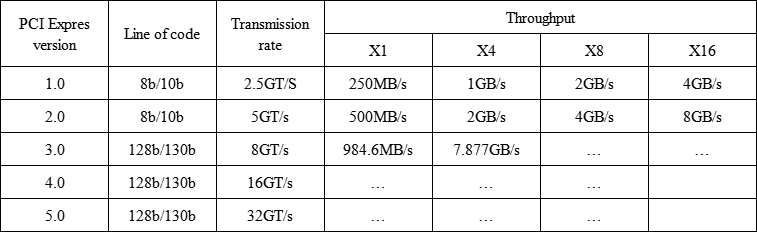

Bandwidth and Data Rate

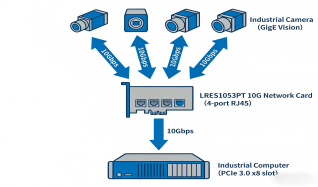

PCIe x1, x2, x4, and x8 refer to different configurations of the PCI Express (Peripheral Component Interconnect Express) bus standard, indicating the number of lanes on the bus。

PCIe X1: Indicates that there is one PCIe lane. The speed of each lane is defined by the PCIe specification, for example, the speed of PCIe 3.0 is 8 Gbps. Therefore, the speed of PCIe X1 is usually 8 Gbps.

PCIe X4: Indicates four PCIe lanes. The speed of each lane is defined by the PCIe specification, for example, the speed of PCIe 3.0 is 8 Gbps. Therefore, the speed of PCIe X4 is usually 32 Gbps (4 lanes x 8 Gbps).

PCIe X8: Indicates eight PCIe lanes. The speed of each lane is defined by the PCIe specification, for example, PCIe 3.0 has a speed of 8 Gbps. Therefore, the speed of PCIe X8 is usually 64 Gbps (8 lanes x 8 Gbps).

When we talk about the transfer rate of the PCIe bus standard, we use GT/s (Giga Transfers per second) instead of Gbps (Giga Bits Per Second). This is because the transfer rate is based on the properties of the physical layer communication protocol and is not related to factors such as link width.

The throughput (available bandwidth) of the PCIe bus can be calculated using the following formula:

Throughput = Transmission rate * Coding scheme

For example, the PCIe 2.0 protocol supports 5.0 GT/s, which means each lane can transmit 5 Gbits per second. However, not every lane supports 5 Gbps because PCIe 2.0 uses an 8b/10b encoding scheme. This means that 10 bits must be sent for every 8 bits transmitted.

Therefore, the rate supported by each lane of the PCIe 2.0 protocol is 5 GT/s * 8 / 10 = 4 Gbps = 500 MB/s.

For example, for a PCIe 2.0 x8 lane, the available bandwidth is 4 Gbps * 8 = 32 Gbps = 4 GB/s.

Similarly, the PCIe 3.0 protocol supports 8.0 GT/s, which means 8G bits can be transmitted per second on each lane. However, PCIe 3.0 uses a 128b/130b encoding scheme, meaning 130 bits must be sent for every 128 bits transmitted.

Therefore, the rate supported by each lane of the PCIe 3.0 protocol is 8 GT/s * 128 / 130 = 7.877 Gbps = 984.6 MB/s.

For example, for a PCIe 3.0 x16 lane, the available bandwidth is 7.877 Gbps * 16 = 126.031 Gbps = 15.754 GB/s.

•ISA ->PCI ->PCIX ->PCIE 1.0 ->PCIE 2.0 ->PCIE3.0 ->PCIE4.0 ->PCIE5.0。

•PCI and PCIX in parallel; PCIE in series。

•PCI Express interfaces include X1, X4, X8, and X16 (X2 mode is used for internal interfaces rather than slot mode). Shorter PCI Express cards can be inserted into longer PCI Express slots。